您现在的位置是:首页 > 行业发展

Spartan-6开发案例使用手册——嵌入式AD模块/接口基础测试(上)

智慧创新站

2025-03-30【行业发展】147人已围观

简介前言本指导文档适用的开发环境为Windows764bit和Windows1064bit。本文档主要提供开发板FPGA端案例测试方法,所有工程均位于产品资料Demo1目录下。进行本文档操作前,请先按照调试工具安装相关文档安装USB转串口驱动、SecureCRT串口调试终端、等相关软件。默认使用FPGA...

本指导文档适用的开发环境为Windows764bit和Windows1064bit。本文档主要提供开发板FPGA端案例测试方法,所有工程均位于产品资料Demo1目录下。进行本文档操作前,请先按照调试工具安装相关文档安装USB转串口驱动、SecureCRT串口调试终端、等相关软件。默认使用FPGARS232作为调试串口,并使用TL-DLC10下载器进行操作演示。

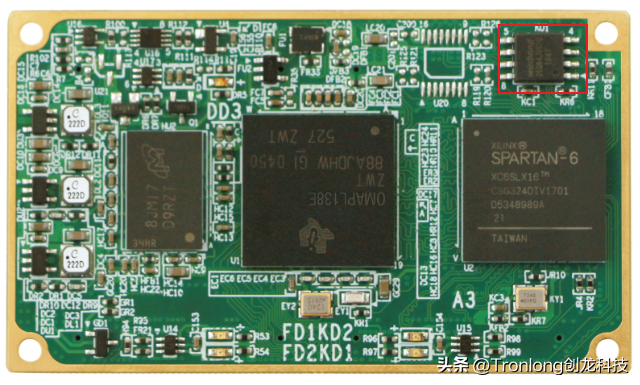

本文测试板卡是TL138/6748F-EVM开发板,它是创龙科技基于Omapl138/TMS320C6748+FPGA核心板开发。由于SOM-TL138F/SOM-TL6748F核心板管脚兼容,所以共用同一个底板。开发板采用核心板+底板的设计方式,尺寸为24cm*13cm,它主要帮助开发者快速评估核心板的性能。

核心板采用高密度8层板沉金无铅设计工艺,尺寸为66mm*38.6mm,板载3路高转换率DC-DC核心电压转换电源芯片,实现了系统的低功耗指标,精密、原装进口的B2B连接器引出全部接口资源,以便开发者进行快捷的二次开发使用。

led_flash——LED测试案例功能:控制开发板底板LED以0.5s间隔闪烁。

表1

开发板

是否支持本案例

TL138F-EasyEVM

支持

TL138F-EVM

支持

TL6748F-EasyEVM

支持

TL6748F-EVM

支持

演示现象

加载或固化程序,开发板底板GD4、GD5、GD6闪烁。

key_test——按键测试案例功能:通过按键控制开发板底板LED的亮灭。

表2

开发板

是否支持本案例

TL138F-EasyEVM

支持

TL138F-EVM

支持

TL6748F-EasyEVM

支持

TL6748F-EVM

支持

演示现象

加载或固化程序,按下按键SW1,GD4将被点亮,再次按下熄灭。

IIC——IIC测试表3

开发板

是否支持本案例

TL138F-EasyEVM

支持

TL138F-EVM

支持

TL6748F-EasyEVM

支持

TL6748F-EVM

支持

案例功能:IIC从设备地址为7'b0101010,寄存器0x01连接到底板FPGA端的LED,寄存器0x02连接到底板FPGA端的按键。DSP通过读取寄存器0x02的值,然后控制寄存器0x01的值,以达到控制FPGA端LED灯的状态。

按钮。

演示现象

FPGARS232串口调试终端打印信息如下图所示:

图1

分别按下按键SW1、SW2、SW3时,对应的GD4、GD5、GD6灯将被点亮。

UART_IP——UART回环测试表4

开发板

是否支持本案例

TL138F-EasyEVM

不支持

TL138F-EVM

支持

TL6748F-EasyEVM

不支持

TL6748F-EVM

支持

案例功能:实现FPGA端的RS232串口回环,使用波特率为115200。

将开发板的FPGARS232和PC机连接,打开串口调试软件。将FPGA端UART_IP程序加载或固化程序进开发板。

演示现象

FPGARS232串口调试终端可回显输入的字符。

图2

uPP_TX——uPP接收测试(DSP接收)表5

开发板

是否支持本案例

TL138F-EasyEVM

支持

TL138F-EVM

支持

TL6748F-EasyEVM

支持

TL6748F-EVM

支持

案例功能:FPGA通过uPP向DSP发送1~2048的数据,每个数据为16位,总共4KB数据。DSP端将接收到数据后在USBTOUART2串口打印出来。

将开发板的USBTOUART2和PC机连接,打开串口调试软件。将FPGA端uPP_TX程序加载或固化进开发板。按照工程导入步骤加载DSP端uPP_A_文件(uPP_A_Receive工程位于TMS320C6748产品资料“Demo\StarterWare\Application\”目录下)。

演示现象

USBTOUART2串口终端将打印以下提示:

图3

按下一次SW1,串口打印信息如下图所示:

图4

upp_loopback——uPP回环测试表6

开发板

是否支持本案例

TL138F-EasyEVM

支持

TL138F-EVM

支持

TL6748F-EasyEVM

不支持

TL6748F-EVM

不支持

案例功能:FPGA将uPPRX接口数据和控制信号线内部回环到TX接口,实现uPP总线的回环通信。

演示现象

请参考OMAPL138产品资料用户手册《OMAPL138基于SYSLINK的双核案例》文档中tl-upp-loopback-test案例测试小节。

bram_emif——EMIFA测试表7

开发板

是否支持本案例

TL138F-EasyEVM

支持

TL138F-EVM

支持

TL6748F-EasyEVM

支持

TL6748F-EVM

支持

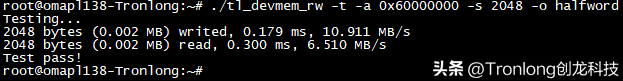

案例功能:通过EMIF接口对FPGA的BRAM进行数据读写。FPGA实现一个16bitASRAM,地址位宽取其底10bit{EMA_A[8:0],EMA_BA[1]},即RAM深度为1024。

EMIF数据在FPGA内部用BRAM缓存,Spartan-6内部BRAM极限工作时钟频率如下图所示:BRAM的时钟说明具体可查看产品资料Xilinx参考文档《ds162Spartan-6FPGADataSheetDCandSwitchingCharacteristics》。BRAM工作时钟由OMAPL138端的emif_clk提供。

图5

演示现象

OMAPL138

为便于测试,案例bin目录已提供开发板可执行文件tl_devmem_rw,将其拷贝到开发板文件系统下,加载或固化FPGA端bram_emif程序后,在tl-devmmem-rw所在路径下执行以下命令。

Target./tl_devmem_rw-t-a0x60000000-s2048-ohalfword

图7

TMS320C6748

请参考TMS320C6748产品资料用户手册《TMS320C6748开发案例使用手册》文档中EMIF_FPGA——EMIFA总线FPGA读写测试案例小节。

AD7606_uPP——AD模块采集测试表8

开发板

是否支持本案例

TL138F-EasyEVM

不支持

TL138F-EVM

支持

TL6748F-EasyEVM

不支持

TL6748F-EVM

支持

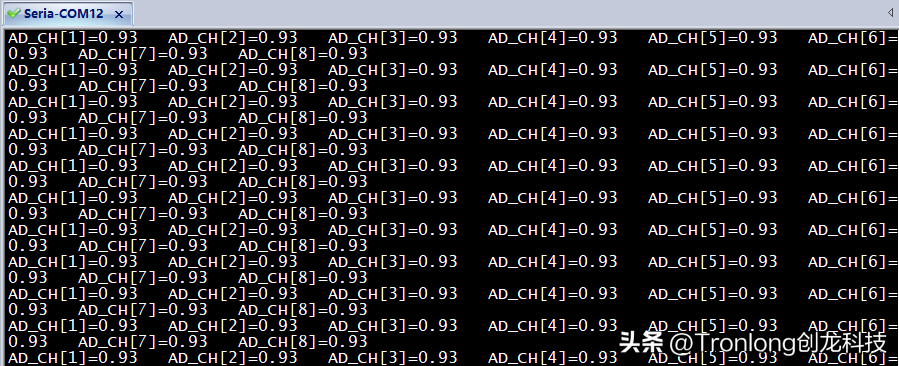

案例功能:将TL7606模块采集的数据通过uPP传回DSP端。

将TL7606模块连接到FPGAExPORT0接口,如下图所示:

图8

将开发板的USBTOUART2和PC机连接,打开串口调试软件。将FPGA端AD7606_uPP程序加载或固化进开发板。按照工程导入步骤加载DSP端uPP_文件(uPP_AD7606工程位于TMS320C6748产品资料“Demo\StarterWare\Application\”目录下)。

演示现象

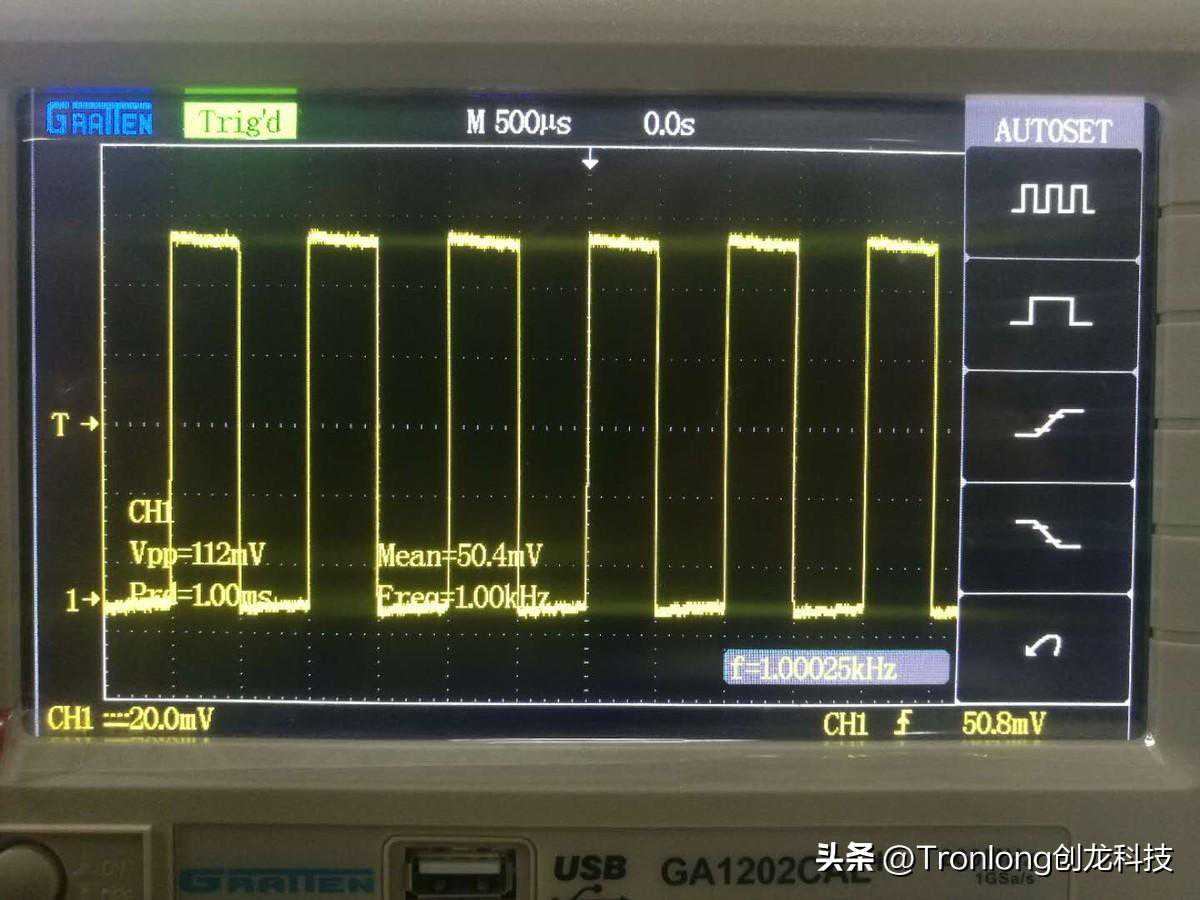

将TL7606模块8个通道接入信号发生源输出通道中,信号发生源设置为1KHz2Vpp的正电压波形。串口终端将打印以下信息:

图9

(2)串口打印信息解析:

AD_CH[N]:通道N;

0.93:通道捕获电压值,单位为V;

通道捕获电压为0.93V,与信号发生源输出电压相近,则测试正常。

注:若测试结果存在偏差,请使用万用表或示波器测量信号发生源输出是否存在偏差。

AD7606x2_uPP——AD模块采集测试表9

开发板

是否支持本案例

TL138F-EasyEVM

不支持

TL138F-EVM

支持

TL6748F-EasyEVM

不支持

TL6748F-EVM

支持

案例功能:将两块TL7606模块共16通道采集的数据通过uPP传输至DSP端,DSP端获取后通过USBTOUART2串口打印出来。

将两块TL7606模块分别连接到开发板FPGAExPORT0、FPGAExPORT1接口。将开发板的USBTOUART2和PC机连接,打开串口调试软件。将FPGA端AD7606_uPP程序加载或固化进开发板。按照工程导入步骤加载DSP端uPP_文件(uPP_AD7606工程位于TMS320C6748产品资料\Demo\StarterWare\Application\目录下)。

演示现象

将TL7606模块1(与FPGAExPORT0接口连接)的8个通道接入信号发生源输出通道中,信号发生源设置为1KHz2Vpp的正电压波形。TL7606模块2(与FPGAExPORT0接口连接)8个通道接入数字电源3.3V。

图10

(2)串口打印信息解析:

AD_CH[N]:通道N;

0.97:通道捕获电压值,单位为V(以TL7606模块1为例);

通道捕获电压为0.97V,与信号发生源输出电压相近,则测试正常。另一个模块打印数据同理。

备注:若测试结果存在偏差,请使用万用表或示波器测量信号发生源输出是否存在偏差。

DDS_UART——多路DA信号输出测试表10

开发板

是否支持本案例

TL138F-EasyEVM

不支持

TL138F-EVM

支持

TL6748F-EasyEVM

不支持

TL6748F-EVM

支持

案例功能:实现多路可调式DA信号电压、方波幅值、方波频率输出,第一路生成正弦波、第二路生成方波、第三路生成三角波、第四路生成锯齿波,每一路可以单独通过串口控制输出频率。

将开发板的FPGARS232和PC机连接,TL5724模块连接到FPGAExPORT0接口,打开串口调试软件。将FPGA端AD8568_UART程序加载或固化进开发板。

演示现象

(1)TL5724模块的四个蓝色指示灯全部点亮;

(2)用示波器可查看四路波形,如图所示:

图11

图12

图13

图14

通过串口调试助手,向开发板FPGARS232串口发送相对应的指令,开发板收到该指令后,进行相应的操作,相应的指令定义如下:

表11

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

其中,Bit7~Bit6为通道控制选择。

表12

Bit7~Bit6

通道选择

00

通道0(正弦波通道)

01

通道1(方波通道)

10

通道2(三角波通道)

11

通道3(锯齿波通道)

Bit5为频率加减控制:数值为1,则对应通道的波形输出频率增加;数值为0,则对应通道的波形输出频率减小。

Bit4~Bit0为频率控制增减值,该值的大小决定了每次频率变化的大小:数值越大,相应通道的输出频率变化越快;数值越小,相应通道的输出频率变化越小。

以通道0(正弦波通道)为例,如图所示:

图15

图16

图17

图18

ADS8568_UART——AD模块采集测试表13

开发板

是否支持本案例

TL138F-EasyEVM

不支持

TL138F-EVM

支持

TL6748F-EasyEVM

不支持

TL6748F-EVM

支持

案例功能:将TL8568模块采集的数据通过FPGA端的串口打印出来。

将TL8568模块连接到FPGAExPORT0接口,如下图所示:

图19

将开发板的FPGARS232和PC机连接,打开串口调试软件。将FPGA端AD8568_UART程序加载或固化进开发板。

演示现象

将TL8568模块8个通道接入信号发生源输出通道中,信号发生源设置为1KHz2Vpp的正电压波形。FPGARS232串口终端打印信息如下图所示:

图20

串口终端可打印输出V0、V1、V2、V3、V4、V5、V6和V7各通道数值,分别对应硬件上的V1~V8通道。支持在串口终端用键盘输入相应字符进行切换通道,如输入V2字符,串口则切换至打印V3通道的数值。

图21

串口打印信息解析:

V0:通道1,(以V1通道为例);

0x0A69:采集数值,计算公式如下:(其中REF为3V);

图22

7FFF转换为十进制:32767;

采样值=32767/(4*REF)*输入电压值=32767/(4*3.0V)=2730=0xAAA,与上述采样值0x0A69(对应十进制:2665)相近,则测试正常。

备注:若测试结果存在偏差,请使用万用表或示波器测量信号发生源输出是否存在偏差。

支持在串口终端配置ADS8568各通道量程。

各通道量程说明如下表所示:

表14

串口输入字符

量程配置

H0

配置V1V2量程为±4VREF

L0

配置V1V2量程为±2VREF

H1

配置V3V4量程为±4VREF

L1

配置V3V4量程为±2VREF

H2

配置V5V6量程为±4VREF

L2

配置V5V6量程为±2VREF

H3

配置V7V8量程为±4VREF

L3

配置V7V8量程为±2VREF

H4

配置V1~V8量程为±4VREF

L4

配置V1~V8量程为±2VREF

在串口终端用键盘输入L4字符时,串口终端打印信息如下:

图23

采样值=32767/(2*VREF)*输入电压值=32767/(2*3.0V)=5461=0x1555,与上述采样值0x14F1(对应十进制:5361)相近,则测试正常。

备注:若测试结果存在偏差,请使用万用表或示波器测量信号发生源输出是否存在偏差。

ADS8568_uPP——AD模块采集测试(使用uPP)表15

开发板

是否支持本案例

TL138F-EasyEVM

不支持

TL138F-EVM

支持

TL6748F-EasyEVM

不支持

TL6748F-EVM

支持

案例功能:将TL8568模块采集回来的数据通过uPP传回DSP端。案例默认设置VREF为3.0V,量程为±4VREF。

将TL8568P模块连接到FPGAExPORT0接口,如下图所示:

图24

将开发板的USBTOUART2和PC机连接,打开串口调试软件。将FPGA端AD8568_uPP程序加载或固化进开发板。按照工程导入步骤加载DSP端uPP_文件(uPP_AD8568工程位于TMS320C6748产品资料\Demo\StarterWare\Application\目录下)。

演示现象

将TL8568P模块的8个通道接入信号发生源输出通道中,信号发生源设置为1KHz2Vpp的正电压波形。串口终端将打印以下信息,如下图所示:

图25

串口打印信息解析:

AD_CH[N]:通道N;

0.96:通道捕获电压值,单位为V;

通道捕获电压为0.96V,与信号发生源输出电压相近,则测试正常。

备注:若测试结果存在偏差,请使用万用表或示波器测量信号发生源输出是否存在偏差。

TL1278_UART——AD模块采集测试表16

开发板

是否支持本案例

TL138F-EasyEVM

不支持

TL138F-EVM

支持

TL6748F-EasyEVM

不支持

TL6748F-EVM

支持

案例功能:将AD模块采集回来的数据通过FPGA端的串口打印出来。

将开发板的FPGARS232和PC机连接,TL1278模块连接到FPGAExPORT0接口,打开串口调试软件。将FPGA端AD1278_UART程序加载或固化进开发板。

演示现象

将信号发生源的负极连接至TL1278模块的AN1接口,正极连接至TL1278模块的AP1接口,信号发生源设置为1KHz2Vpp的正电压波形,FPGARS232串口终端打印信息如下图所示:

图26

保持硬件连接不变情况下,信号发生源设置为1KHz2Vpp的负电压波形,串口终端打印信息如下图所示:

图27

采集电压值计算

计算公式如下表所示:

图28

采集正电压值计算(以CH1通道为例):

CH1:通道1

0x349B5F:采集数值,计算公式如下:(其中REF为2.5V)

7FFFFF转换为十进制:8388607

采样值=8388607*输入电压值/REF

0x349B5F转化为十进制为3447647,代入上述公式为:3447647=8388607*输入电压值/2.5

则输入电压值为:输入电压值=3447647*2.5/8388607=1.027V,与信号发生源输出电压相近,则测试正常。

备注:若测试结果存在偏差,请使用万用表或示波器测量信号发生源输出是否存在偏差。

采集负电压值计算(CH1通道为例):

CH1:通道1

0xD23A4D:采集数值,计算公式如下:(其中REF为2.5V)

FFFFFF转换为十进制:16777215

采样值=16777215+8388607*输入电压值/REF

0xD23A4D转化为十进制为13777485,代入上述公式为:13777485=16777215+8388607*输入电压值/2.5

则计算出输入电压值为:输入电压值=(13777485-16777215)*2.5/8388607=-0.893V,,与信号发生源输出电压相近,则测试正常。

备注:若测试结果存在偏差,请使用万用表或示波器测量信号发生源输出是否存在偏差。

TL1278_uPP——AD模块采集测试(使用uPP)表17

开发板

是否支持本案例

TL138F-EasyEVM

不支持

TL138F-EVM

支持

TL6748F-EasyEVM

不支持

TL6748F-EVM

支持

案例功能:将TL1278模块采集回来的数据通过uPP传回DSP端。

将TL1278模块连接到FPGAExPORT0接口,开发板的USBTOUART2和PC机连接,打开串口调试软件。将FPGA端ADS1278P_uPP程序加载或固化进开发板。按照工程导入步骤加载DSP端FPGA_文件(FPGA_ADS1278工程位于TMS320C6748产品资料“Demo\SYSBIOS\Application\”目录下)。

演示现象

将信号发生源负极连接至TL1278模块AN1接口,信号发生源正极连接至TL1278模块AP1接口,信号发生源设置为1KHz2Vpp的正电压波形。USBTOUART2串口终端打印信息如下图所示:

图29

保持硬件连接不变情况下,信号发生源设置为1KHz2Vpp的负电压波形。串口终端打印信息如下图所示:

图30

采样电压计算

计算公式如下表所示:

图31

采集正电压值计算(以CHANEL_1通道为例):

CHANEL_1:通道1;

3442710:采集数值,计算公式如下:(其中REF为2.5V);

7FFFFF转换为十进制:8388607;

采样值=8388607*输入电压值/REF;

将串口输出采样值代入上述公式为:3442710=8388607*输入电压值/2.5;

计算出输入电压值为:输入电压值=3442710*2.5/8388607=1.026V,与信号发生源输出电压相近,则测试正常。

备注:若测试结果存在偏差,请使用万用表或示波器测量信号发生源输出是否存在偏差。

采集负电压值计算(以CHANEL_1通道为例):

由于DSP程序已对数据进行初步转换,所以这里可以按照正电压计算方式计算。

CHANEL_1:通道1;

-3004502:采集数值,计算公式如下:(其中REF为2.5V);

7FFFFF转换为十进制:8388607;

采样值=8388607*输入电压值/REF;

将串口输出采样值代入上述公式为:-3004502=8388607*输入电压值/2.5;

计算出输入电压值为:输入电压值=-3004502*2.5/8388607=-0.895V,与信号发生源输出电压相近,则测试正常。

备注:若测试结果存在偏差,请使用万用表或示波器测量信号发生源输出是否存在偏差。

AD采集三核通信案例测试表18

开发板

是否支持本案例

TL138F-EasyEVM

不支持

TL138F-EVM

支持

TL6748F-EasyEVM

不支持

TL6748F-EVM

不支持

若无特殊说明,本节案例适用于TL8568P模块和TL7606P模块。默认使用TL8568模块进行测试,FPGA端加载或固化ADS8568_uPP程序;若使用TL7606模块,FPGA端加载或固化AD7606_uPP程序即可。

完成以下测试之前,请先参考OMAPL138产品资料的《OMAPL138的多核软件开发组件MCSDK开发入门》、《OMAPL138相关软件安装》、《OMAPL138基于IPClite双核裸机案例》、《基于OMAPL138开发板的LinuxQT图形界面开发入门教程》和《OMAPL138基于SYSLINK的双核案例》指导文档,完成MCSDK组件、Linux版本软件、Linux版本Starterware组件、ARM端Qt和qwt组件的安装和编译。

表19

指导文档

软件组件

OMAPL138的多核软件开发组件MCSDK开发入门

MCSDK组件

OMAPL138相关软件安装

Linux版本软件

OMAPL138基于IPClite双核裸机案例

Linux版本Starterware组件

基于OMAPL138开发板的LinuxQT图形界面开发入门教程

ARM端Qt

OMAPL138基于SYSLINK的双核案例

qwt组件

将OMAPL138产品资料Images目录下的hw_文件,替换Linux版本Starterware安装路径"/home/tl/OMAPL138_StarterWare_1_10_04_01/include/hw"下的hw_文件,如图所示。

图32

替换后的.h文件内容,如图所示。

图33

打印AD采集的数据案例功能:AD模块以500K的速率进行8通道采样,并通过uPP将数据传递到DSP端,ARM端打印DSP接收到的V1通道的数据。

操作步骤

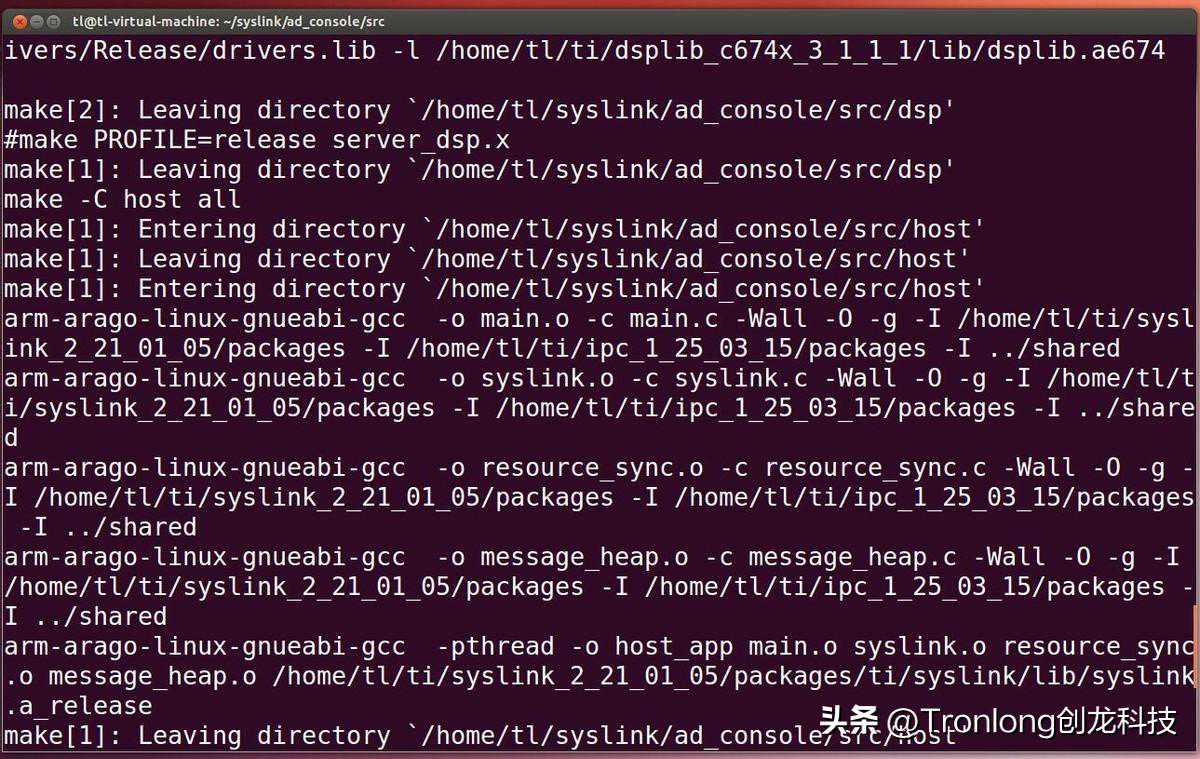

编译源码

源码位于OMAPL138产品资料"Demo\syslink\ad_console\src"目录下,拷贝源码到Ubuntu下,并进入到目录。

根据实际情况修改"host/makefile"里的MCSDK开发包路径:

Hostgeditdsp/makefile

图35

MCSDK=/home/tl/ti//MCSDK安装路径

CCS=/home/tl/ti//CCS安装路径

STARTWARE_INSTALL_DIR=/home/tl/OMAPL138_StarterWare_1_10_04_01

//StarterWare安装路径

使能MCSDK集成的交叉编译环境,对工程进行编译。

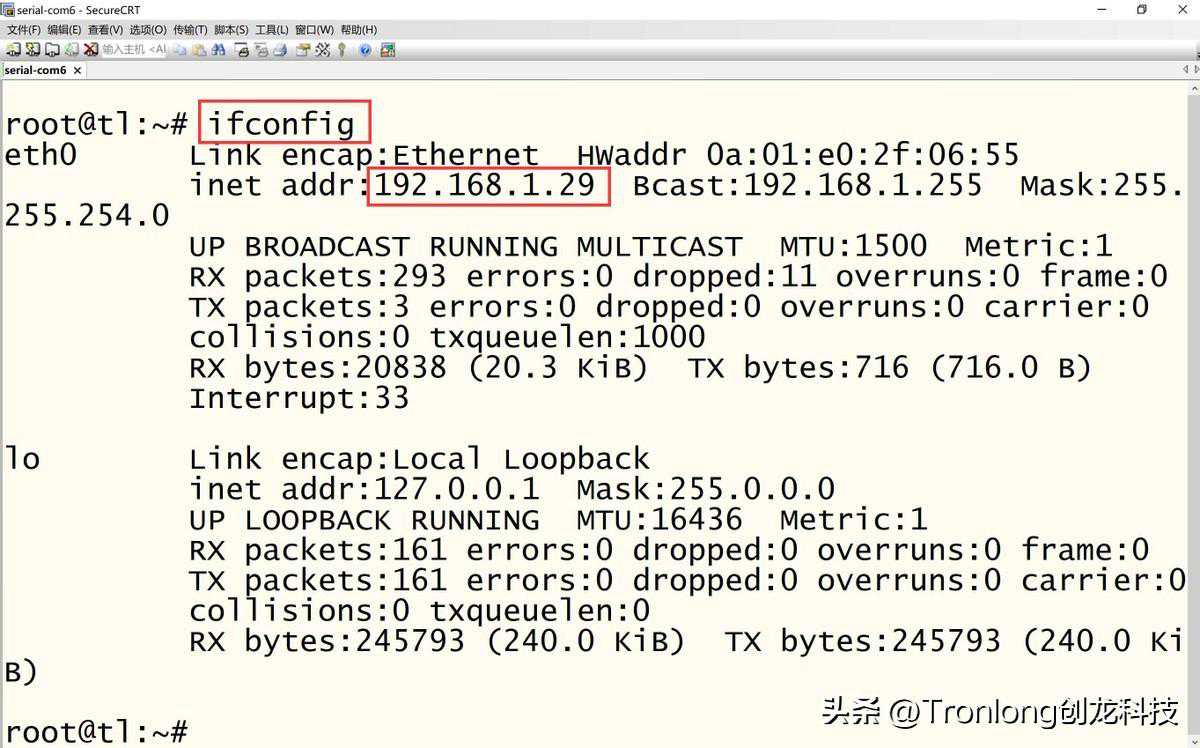

Hostmakeclean

Hostifconfig

图40

图41

图42

图43

图44

在ssh网络控制终端进入工程的run目录,执行,命令如下:

备注:请根据实际路径进行操作。

Target2./

图45

图46

串口终端打印信息,如下图所示。

图47

很赞哦!(93)

上一篇:如何写技术规格书?

下一篇:微软推出自家阅后即焚服务