您现在的位置是:首页 > 智能机电

来看看与非门内部结构,是如何运算的

智慧创新站

2024-11-09【智能机电】243人已围观

简介与非门原来是这样。这个就是数电里面一个简单的门电路,想要知道是它的什么门?首先q1与q3是两个串联的mos,q2与q4是两个并联的pmos,这两端是信号的输入端,也就是逻辑控制的输入端,ab两个点,右边就是门电路的输出,用q来表示,来看一下是怎么运算的。其实知道对于一个门电路来说,输出的电位无非就是...

与非门原来是这样。

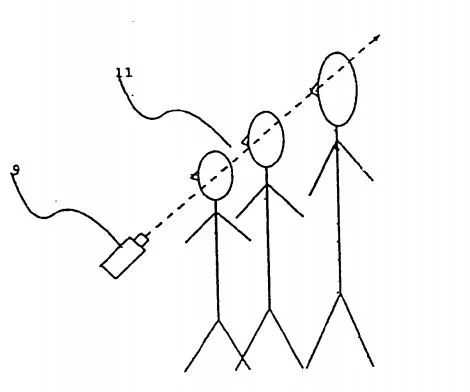

这个就是数电里面一个简单的门电路,想要知道是它的什么门?首先q1与q3是两个串联的mos,q2与q4是两个并联的pmos,这两端是信号的输入端,也就是逻辑控制的输入端,ab两个点,右边就是门电路的输出,用q来表示,来看一下是怎么运算的。

其实知道对于一个门电路来说,输出的电位无非就是一个高,一个是低。高电位也就是上拉到电源电压vdd,也就最高到达电源电压vdd,最低就是下拉到地电位,也就是gnd,只会在这两个值之间变化。

怎么样才能让它输出一个低电位?也就是将输出信号直接拉到地。因为看到q1与q3是串联的关系,只有两个一三同时导通,这时候输出才会有机会被拉到地。但是光靠这两个导通还不够,这时候上面这两个pmos管q2与q4必须是截止的状态,只有这样电源电压才不会跑到输出端。

所以控制了逻辑就非常清楚了,要一三导通,二四截止,所以输入端的两个信号都要输入一个高电位,这样q1与q3同时导通,因为24是一对pmos管,当a、b是高电位的时候,它们就是截止的状态,这时候输出就是一个低电位。

输出高电位就很简单,只要把输入的两端都变成低电位,这时候一三截止,二四导通,这时候输出信号没有办法下拉到地,相反电源电压可以跑到输出端,也就是上拉到电源电压,这时候就会输出一个高电位。可以看到它们依然是一个逻辑反相的关系,当控制信号是高,输出就是低,当控制信号两个都是低的时候,这时候输出的电位就是高电位。

现在就有一个问题了,假设a输入端是一个低电位,b是高电位,第三组状态,假如a是低电位,b是高电位,这时候输出的信号,q的状态是怎么样的?a是低电位,也就是q3是截止,b是高电位,也就是q1是导通的。但是由于q1、q3是串联起来的,只要有其中一个截止,信号都是没有办法直接拉到地的,所以下拉的这一路依然是断开的状态。

再来看上拉的,当a是低电位,q2导通,q4截止。虽然这时候q4截止,因为q2与q4是并联起来的,只要有一路导通,电源电压就可以跑到输出端,所以这时候输出信号就被直接上拉到电源电压,也就输出一个高电位,所以这时候输出的q应该是一个高电位。

反过来假设a是高电位,b是一个低电位,同样的这时候q3导通,q1截止,它们串联的状态依然是截止的状态,但是q2与q4其中的q4是导通,这样即使q2是截止,输出信号依然可以被拉到电源电压,这个vdd,所以输出依然是一个高电位。

所以什么情况下输出才会是一个低电位?只有ab同时都是高电位,也就是q1与q3同时导通,q2和q4同时截止,这样才有可能输出一个低电位。这种情况两个都是高电位才可以输出一个低电位,两个低电位就会输出一个高电位。

所以这个电路会实现一个什么功能?实现是一个这样的运算,输出q是等于a与上b只有两个同时都是高电位,这时候才会输出一个反相的低电位。所以这里还有一个非,也就是它是一个与非门。

很赞哦!(79)