您现在的位置是:首页 > 创新技术

verilog实例(五)

智慧创新站

2024-12-09【创新技术】234人已围观

简介本文介绍一些verilog实现的数字电路的实例。如有错误,欢迎指出,感谢。124进制计数器实验原理:使用两位数码管显示24进制计数器,每次只选择一位位选,然后在1khz-十几khz可以让人眼反应不过来,然后达到每次仿佛显示两位的效果,然后段选是在每个位选选通的时候就送入一个段选即可。Experime...

本文介绍一些verilog实现的数字电路的实例。如有错误,欢迎指出,感谢。

1

24进制计数器

实验原理:使用两位数码管显示24进制计数器,每次只选择一位位选,然后在1khz-十几khz可以让人眼反应不过来,然后达到每次仿佛显示两位的效果,然后段选是在每个位选选通的时候就送入一个段选即可。

Experimentalprinciple:theuseoftwodigitaltubedisplay24basecounter,eachtimeonlyselectabit,andthenin1khz-tenKHZcanmakethehumaneyecannotreact,andthenachievetheeffectoftwodisplayeachtime.

核心代码:

Thecorecode:

波形:

wave:

2

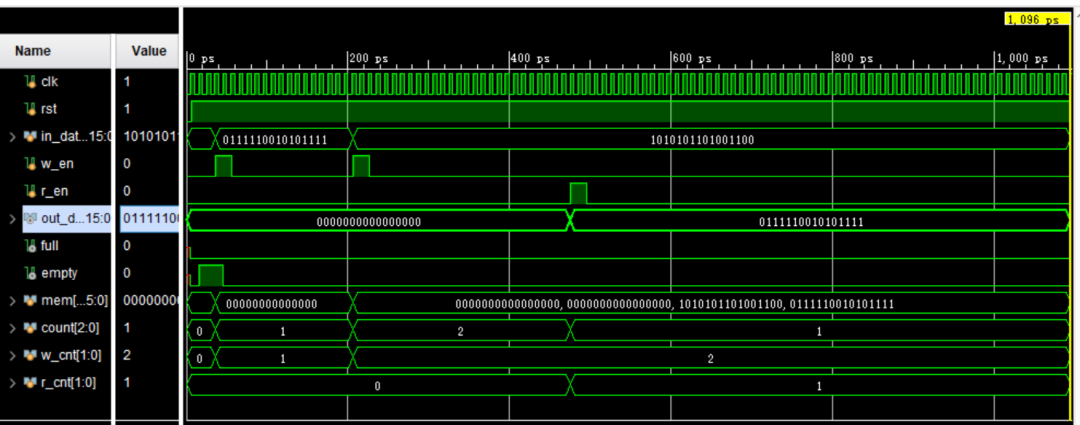

同步FIFO

实验原理:FIFO分为同步和异步,这里介绍同步,FIFO存储器是系统的缓冲环节,其功能可以概括为对连续的数据流进行缓存,防止在进机和存储操作时丢失数据,数据集中起来进机和存储,可避免频繁的总线操作,减轻CPU的负担。

Experimentalprinciple:FIFOisdividedintosynchronousandasynchronous,synchronizationisintroducedhere,FIFOmemoryisthebufferlinkofthesystem,itsfunctioncanbesummarizedasthecontinuousdataflowcache,preventthelossofdatainthemachineandstorageoperation,datacentralizedintothemachineandstorage,canavoidfrequentbusoperation,reducetheburdenofCPU.

核心代码:

Thecorecode:

波形:

wave:

3

UART发送12位数据

实验原理:使用状态机对状态进行切换,使用移位寄存器接收满了8位数据后就重新发送标志位,并重新开始接收。

Usethestatemachinetoswitchthestate,usetheshiftregistertoreceivefull8bitsofdataonthere-sflagbits,andstartreceivingagain.

核心代码:

Thecorecode:

波形:

wave:

参考资料:

《FPGA/CPLD边学边练》吴厚航著

百度

翻译:谷歌翻译

很赞哦!(102)