您现在的位置是:首页 > 行业发展

基于FPGA的数字电路实验4:采用模块化思路设计一个译码器

智慧创新站

2025-01-14【行业发展】164人已围观

简介由于篇幅有限,我们用一个3-8译码器来结束本次对组合逻辑电路的介绍,并且最后我们还给大家准备了一个略微酸爽的任务,确保大家的脑神经都可以得到充分的摩擦。闲话不多说,现在开始。本次实验的任务是构建一个3-8译码器,且将译码结果通过小脚丫的LED灯显示。听上去并不难,而且我能想象到,一定会有不少同学会立...

由于篇幅有限,我们用一个3-8译码器来结束本次对组合逻辑电路的介绍,并且最后我们还给大家准备了一个略微酸爽的任务,确保大家的脑神经都可以得到充分的摩擦。闲话不多说,现在开始。

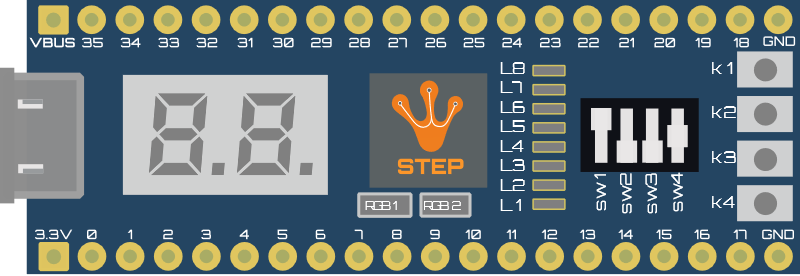

本次实验的任务是构建一个3-8译码器,且将译码结果通过小脚丫的LED灯显示。

听上去并不难,而且我能想象到,一定会有不少同学会立刻开始画一个8行的真值表,然后通过卡诺图进行化简,且根据最终的逻辑表达式画出门电路图。这个方法当然没有错,不过,如果面对更多位数的系统,比如4-16或者是8-256的译码器,建一个几百行的真值表并进行逻辑运算听上去似乎不那么科学。

在这里我们将采用模块化的思路来完成我们的实验设计。

在开始进行模块化设计之前,我们先做一个2-4译码器,也就是译码器系列中最底层的基础模块。

A1

A0

Y3

Y2

Y1

Y0

0

0

0

0

0

1

0

1

0

0

1

0

1

0

0

1

0

0

1

1

1

0

0

0

这次的代码我们采用行为级描述(Behavioral-level)的写法,直接根据真值表将输入与输出的各种组合进行直接关联。可以看出,行为级的写法甚至不需要构建门电路,仅通过输入输出对应关系即可构建,因此最为抽象,同时也意味着更快的运算速度?。

moduledecode24

(

inputwire[1:0]A,//定义两位输入

outputreg[3:0]Y//定义输出的4位译码结果对应的led

);

always@(A)//always块语句,a值变化时执行一次过程块

begin

case(A)

2'b00:Y=4'b0001;//2-4译码结果

2'b01:Y=4'b0010;

2'b10:Y=4'b0100;

2'b11:Y=4'b1000;

case

module

有了最基础的模块,如何通过它搭建出3-8译码器呢?现在,我们在原有的真值表上加上一路使能信号E,再来观察一下新的真值表。可以发现,当E为低电平时,不论输入的取值如何,前四位输出均为0。当E为高电平时,右侧仍然为2-4译码器的输出结构。

E

A1

A0

Y3

Y2

Y1

Y0

0

X

X

0

0

0

0

1

0

0

0

0

0

1

1

0

1

0

0

1

0

1

1

0

0

1

0

0

1

1

1

1

0

0

0

我们可以把表3看作为一个3-8译码器的真值表,只不过输入端的最高位由E代替。由于E为低电平时输出最高的四位均为0,因此确保我们在对后四位输出(黄色)进行赋值不会影响到前四位的输出。

A2

A1

A0

Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

E

A1

A0

Y3

Y2

Y1

Y0

y3

y2

y1

y0

0

0

0

0

0

0

0

0

0

0

1

0

0

1

0

0

0

0

0

0

1

0

0

1

0

0

0

0

0

0

1

0

0

0

1

1

0

0

0

0

1

0

0

0

1

0

0

0

0

0

1

0

0

0

0

1

0

1

0

0

1

0

0

0

0

0

1

1

0

0

1

0

0

0

0

0

0

1

1

1

1

0

0

0

0

0

0

0

从表3不难看出,黄框和红框对应的其实就是一个带有使能端的2-4译码器,且使能端E控制着前后半端位数的输出结果。也就是说,一个3-8译码器可以由两个2-4译码器构成。同理,一个4-16译码器可以由两个3-8译码器构成,以此类推。

带有使能E的2-4译码器如下图所示。实际上就是在之前的代码上稍做修改,在这里我们就不详细写出来了,给大家自行练习的机会。

接下来,按照之前的分析,我们画出由两个2-4译码器组成的3-8译码器的结构。

以下是用Verilog写的一个3-8译码器,在程序里我们调用了两次2-4译码器的子模块。注意,子模块的文件需要和decode38文件放在同一个工程目录下,不然就成了隔壁老王了。

moduledecode38

(

inputwire[2:0]X,

outputwire[7:0]D

);

decode24upper//调用第一个子模块,命名为upper

(

.a(X[1:0]),//将大模块的X1,X0与lower的A1,A0匹配

.E(X[2]),//将大模块的X2与lower的E匹配

.Y(D[7:4])//将大模块的D7-D4与lower的Y3-Y0匹配

);

decode24lower//调用第二个子模块,命名为lower

(

.a(X[1:0]),//将大模块的X1,X0与lower的A1,A0匹配

.E(!X[2]),//将大模块的X2与lower的E匹配

.Y(D[3:0])//将大模块的D7-D4与lower的Y3-Y0匹配

);

module

当你反复在图和代码之间徘徊几轮,并有了多么痛的领悟之后,你就可以把自己编译好的程序下载到小脚丫里,然后通过实验测试你的代码了。

练习一下,当我们把输出D7-D1分别对应为小脚丫上的L7-L1,且输入X2-X0分别对应至小脚丫的SW3-SW1,请判断以下的LED状态。

在倒腾了半天之后,你终于搞定了代码,并且成功在小脚丫上验证了你的设计,于是满怀信心的你终于可以洗洗睡了就可以尝试一下通过模块化的设计思路去构建4-16甚至更多位的译码器了。

当然~我知道你们是不会真的再去老老实实写程序的,所以咱就在这里提几个简单的问题,你们自己做做样子思考一下就完事儿了。

Q1:构建4-16译码器需要几个3-8译码器?答曰:

Q2:构建4-16译码器需要几个2-4译码器?答曰:

Q3:构建5-32译码器需要几个2-4译码器?答曰:

Q4:小明家一个4-16的译码器200块,小李家2-4译码器卖50块,现在你需要一个4-16的译码器,你会怎么选择:

A:去小明家买

B:去小李家买

C:举报他俩竟敢卖这么贵

D:元器件厂商的一些朋友立刻从海拔下八千米冒了出来并打出了他们家的广告

很赞哦!(161)