您现在的位置是:首页 > 智能机电

verilog实例(三)

智慧创新站

2024-12-04【智能机电】126人已围观

简介本文介绍一些verilog实现的数字电路的实例。如有错误,欢迎指出,感谢。1乒乓操作实验原理:在一个数据进行缓存的时候,另一个数据进入数据流选择单元就可以减少延时,让各个模块同时工作。Experimentalprinciple:Whenonedataiscached,anotherdataenter...

本文介绍一些verilog实现的数字电路的实例。如有错误,欢迎指出,感谢。

1

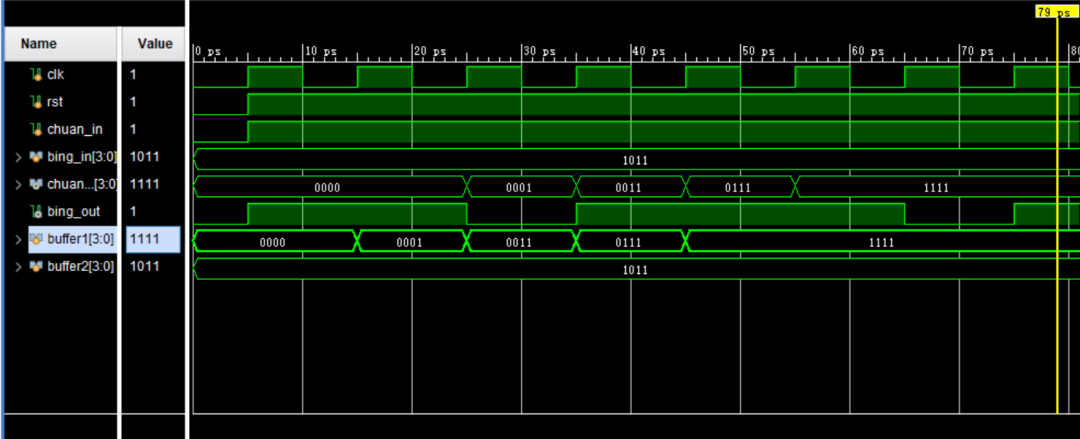

乒乓操作

实验原理:在一个数据进行缓存的时候,另一个数据进入数据流选择单元就可以减少延时,让各个模块同时工作。

Experimentalprinciple:Whenonedataiscached,anotherdataentersthedatastreamselectionunittoreducethedelayandalloweachmoduletoworkatthesametime.

代码:

code:

波形:

wave:

2

流水线

实验原理:以并行的进行单向数据流处理,提高数据处理速度,将一个很长的组合逻辑可以进行拆分,让其并行执行。

Experimentalprinciple:One-waydatastreamprocessingisperformedinparalleltoimprovedataprocessingspeed,andalongcombinationallogiccanbesplitandexecutedinparallel.

核心代码:

corecode:

波形:

wave:

3

串并转换

实验原理:进行串入并出或者并入串出的操作,串入并出就可以设置一个缓存器和计数器,每个时钟周期里面就把数据存入,通过判断计数器的值等待数据存完后就可以进行输出了,并入串出可以将数据存入一个缓存器后在每个时钟周期进行移位,等待计数器计到某个值后就停止移位。

Experimentalprinciple:performserial-in-parallel-outorparallel-in-serial-outoperations,abufferandacountercanbesetupforserial-in-parallel-out,andthedataisstoredineachclockcycle,,andtheparallelinputandserialoutputcanstorethedatainabufferandshiftiteveryclockcycle,andstopshiftingafterwaitingforthecountertocounttoacertainvalue.

参考资料:

《FPGA/CPLD边学边练》吴厚航著

百度

翻译:谷歌翻译

很赞哦!(26)